# Leonardo da Vinci

## Pilot Project No: CZ/02/B/F/PP/134001

## Course on Dynamics of multidisplicinary and Controlled Systems

Part II Modelling of Semiconductor Devices October 14, 2004

> Christoph Clauss, Karl-Heinz Diener, Peter Trappe Fraunhofer-Institut für Integrierte Schaltungen Branch Lab Design Automation 01069 Dresden, Germany http://www.eas.iis.fhg.de

# Contents

| 1        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| <b>2</b> | Inserting a Device Model into DYNAST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |  |  |  |  |  |  |  |  |  |

| 3        | Electronics of Semiconductor Structures         3.1       Charge carriers in semiconductor electronics         3.1.0       Constants of semiconductor electronics         3.1.1       Electrons and holes in doped semiconductors         3.1.2       Energy-band diagram         3.1.3       Energy and potential dependency of charge carriers         3.1.4       Temperature dependency of the charge carrier density         3.1.5       Recombination         3.2       Electric field and space charges in semiconductors         3.3.0       Summary         3.3.1       Field drift and diffusion currents         3.3.2       Carrier flow and the continuity equations                                                                                        | <b>17</b><br>18<br>18<br>20<br>24<br>26<br>27<br>28<br>30<br>30<br>30<br>31<br>34                   |  |  |  |  |  |  |  |  |  |

| 4        | pn-Junction and Diodes4.1Basics of the operation principle<br>4.1.04.1.0Summary<br>4.1.14.1.1Field and potential distribution in diodes4.2Space charge capacitance4.3I/V-characteristic4.4Dynamics of pn -junction (diode)4.5Large-signal network model4.6Thermal behavior4.7Problems and examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>35</b><br>36<br>36<br>42<br>44<br>49<br>51<br>52<br>53                                           |  |  |  |  |  |  |  |  |  |

| 5        | Bipolar Transistors         5.1 Function principles of bipolar transistors         5.1.0 I/V-characteristic         5.1.1 The Ebers-Moll model         5.1.2 Dynamical effects and capacitances         5.12 Advanced models of bipolar transistors         5.2 Advanced models of bipolar transistors         5.2.0 Real structures of bipolar transistor         5.2.1 Transport model         5.2.2 Gummel-Poon model         5.2.2.1 Stored Charges of Injected Minority Carriers         5.2.2.2 Depletion Charges of the Junctions - Early Effect         5.2.2.3 Implementation of the Base Charge in the Gummel-Poon Model         5.3 Special effects         5.4 Temperature effects         5.5 The Spice Gummel-Poon Model         5.6 Problems and examples | <b>57</b><br>58<br>60<br>61<br>62<br>63<br>66<br>66<br>67<br>67<br>67<br>68<br>69<br>69<br>70<br>74 |  |  |  |  |  |  |  |  |  |

| 6 | мо  | S field                 | -effect transistors                                | 79  |

|---|-----|-------------------------|----------------------------------------------------|-----|

|   | 6.1 | Energ                   | y-band diagram of the MOS transistor structure     | 80  |

|   |     | 6.1.0                   | Summary                                            | 80  |

|   |     | 6.1.1                   | MOS transistor structure under thermal equilibrium | 80  |

|   |     | 6.1.2                   | Field-effect control                               | 82  |

|   | 6.2 | Contro                  | ol charges in the NMOS transistor                  | 85  |

|   |     | 6.2.0                   | Summary                                            | 85  |

|   |     | 6.2.1                   | Field-effect based conductivity and charge control | 86  |

|   | 6.3 | Opera                   | tion Principles of MOS Transistors                 | 88  |

|   |     | 6.3.0                   | Summary                                            | 88  |

|   |     | 6.3.1                   | Types of MOS transistors                           | 88  |

|   | 6.4 | I/V-cł                  | naracteristic for strong inversion                 | 89  |

|   |     | 6.4.0                   | Summary                                            | 89  |

|   |     | 6.4.1                   | Unipolar channel current                           | 90  |

|   |     | 6.4.2                   | Thermal effects                                    | 92  |

|   | 6.5 | Large-                  | signal network model                               | 94  |

|   |     | 6.5.0                   | Summary                                            | 94  |

|   |     | 6.5.1                   | Model architecture                                 | 95  |

|   |     | 6.5.2                   | Large-signal DC model                              | 96  |

|   |     | 6.5.3                   | Large signal model's capacitances                  | 96  |

|   | 6.6 | $\operatorname{Proble}$ | ems and examples                                   | 100 |

| 7 | Ref | erence                  | s                                                  | 105 |

| 8 | Ans | wers t                  | o Self-Assessment Questions                        | 107 |

# Module 1

# Introduction

To become competitive at markets, today, innovative system solutions for new products have to be based on key technologies as electronics, microelectronics, telecommunication and micro-electro-mechanical systems (MEMS). Actually, the technical progress in these key technologies proceeds rapidly. Therefore, classical education at universities has to be accomplished by additional learning activities, particularly focused on

- Life-long learning in companies and research institutions

- Assisting classical teaching courses to improve the learner's motivation

- Imparting short-lived knowledge distilled from latest R & D activities.

To cope with the enormous increase of knowledge day for day on the one hand, and the limited time to impart it on the other hand, multi-media-based learning facilities become more and more important. In particular, the Web-based education methodology offers new chances and challenges. Indeed, Internetbased techniques have set up the technical basis to meet the demands for flexibility in learning at different places and at any time as well as updating the short-lived knowledge.

In fact, simulation has proved as a very important method to perform virtual experiments to get deeper understanding of interdisciplinary processes, and to gain insight in complex systems aimed at verifying and optimizing new designs and developments. Therefore, simulation should be an integral part in classic teaching mainly relied on face-to-face courses as well as in engineering.

This widespread spectrum of applications is one of many other reasons to provide powerful simulation facilities.

In this sense, the interactive simulator Dynast http://virtual.cvut.cz/cacsd/msa/onlinetools.shtml developed at the Czech Technical University in Prague which can be used via the Internet is an appropriate simulation tool.

Dynast is the software basis of a Web-based course on Dynamics and Control of Multidisciplinary Engineering Systems (DynLAB). Partners in four countries are developing this course under the umbrella of the European Leonardo project. The multidisciplinary modeling and simulation strategy is strongly focused on a very general "multipole approach" that has been proved successfully for years.

Generally, the development of mixed electrical and non-electrical systems as well as electronic solutions for new product waves is mainly based on design-driven simulations. Therefore, the Dynast simulator has to be provided with a suit of models for semiconductor devices (e.g. diodes, MOS and Bipolar transistors). Semiconductor devices are the main item in modern circuitry, either in a complex net of discrete electronic devices (capacitors, inductors, resistors and transistors, etc.), or as integrated circuits (IC) on semiconductor chips. Basically, diodes and transistors exhibit a nonlinear current/voltage (I/V) characteristic. That is why already pretty simple circuits cannot be understood completely without a detailed analyze. This can be done by simulation with Dynast. Basically, four fields of using Dynast may be highlighted in the following:

- 1. The user (or learner) is mainly interested in analyzing a given and developed circuit, respectively. In this case, he needs stable device models capable to describe all essential effects to meet the circuits functionality. Therefore, a set of models for different demands (simple models until advanced models) should be available. The user's (learner or engineer) main interest is focused on how to specify the model's parameters to simulate the circuit under test successfully.

- 2. The user (mostly designers and engineers) has to find out why his circuit does not meet all characteristic parameters as specified. In this case, he has to identify what the weak points are, and how to cancel them. In this case, the electronic devices have to be included in the failure consideration. That requires more information on device parameters to be specified before simulation. In particular, the users are interested in their impact on the device's internal electronics. Often, the problems arisen in the circuit under development are due to thermal effects. Typically, power dissipation can shift temperature sensitive parameters of the semiconductor devices resulting in breaking down the circuit's functionality. To identify such thermal effects it is very important to have available device models with a thermal pin. Therefore, critical heating effects can be identified by simulations and minimized before manufacturing the circuits.

- 3. The user is compelled to include his own model (company specific models) into the Dynast simulation environment. In this case, he needs all relevant information to implement his models correctly.

- 4. Web-based course on Dynamics and Control of Multidisciplinary Engineering Systems has been set up for assisting classical teaching courses with virtual experiments to improve the learners' motivation to deal with complex physical phenomena more in detail. Moreover, it is aimed at performing professional training in companies and also for in-house qualification activities.

Based on appropriate advanced models, Dynast also offers the chance to provide engineers with leading edge as well as fast moving knowledge. Thus, Dynast will bridge the gap between the basics mainly imparted at universities and interdisciplinary expertise necessary for mastering the design processes in key technologies as electronics and micro-electro-mechanical systems (MEMS).

The course "Modelling of Semiconductor Devices" is indented to fulfill these entire goals.

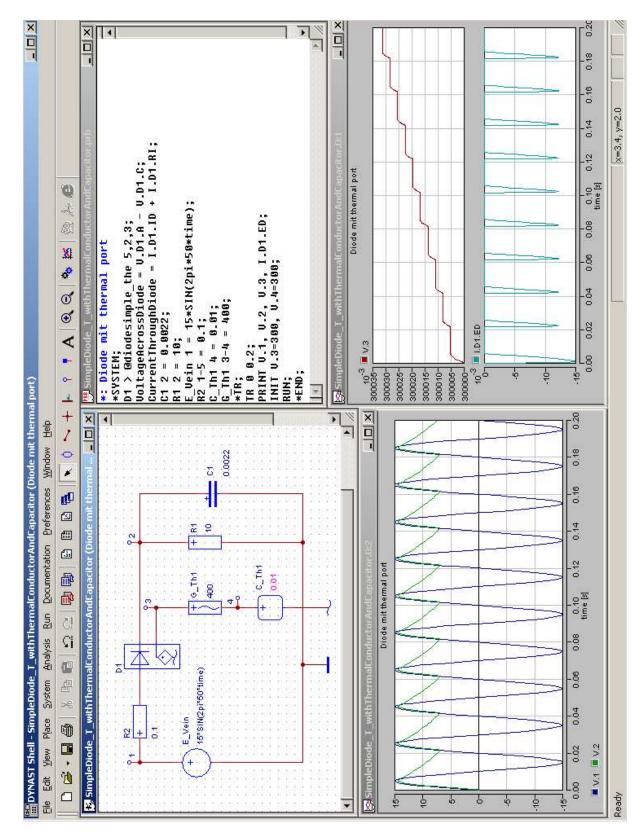

Figure 1.1: Dynast simulation: schematic entry, simulation control, and results

## Module 2

# Inserting a Device Model into DYNAST

Module overview. Granted that a user wants to create a new transistor model into the DYNAST simulator. In this module it is described step by step what has to be done to insert a transistor model if the formula is given.

The very simple model is chosen in view of transistor models that are commonly in use, especially in DYNAST.

Module objectives. When you have completed this module you should be able to:

- 1. Insert an own model into DYNAST

- 2. Use his model within simulation experiments

Module prerequisites. DYNAST installation, basic experience in using DYNAST

As an example we take an oversimplified model with the pins G (gate), D (drain) and S (source). The drain-source-current  $i_t$ r is equal to

#### i\_tr = if vg>p1 then (vd -vs) p2 else (vd - vs)\*p3

with vd - drain voltage, vs - source voltage, vg - gate voltage, and p1, p2, and p3 parameters. The gate current is zero.

The following steps have to be carried out:

#### 1. Start the DYNAST shell

#### 2. Create a model file

```

Press File > New

In the following window choose :

File type: submodel text

File name: T_Example

Model: simple transistor example

Choose the documentation template.

Press OK

```

A window with a general template for a model appears where the text can be edited:

| BDYNAST Shell - T_Example.mod                                                              |         |

|--------------------------------------------------------------------------------------------|---------|

| Eile Edit Yiew System Errors Documentation Run Preferences Window Help                     |         |

| D ☞ - E 番   3 h f C   2 C   💀 🥵   E I H B 🗟 号   🍋 👫 👫 🦄 🗰 Txx MF 🗰   🕸 ½ 🥴                 |         |

| T_Example.mod                                                                              |         |

| :: <enter description="" here="" module=""></enter>                                        | =       |

| :::SYMB                                                                                    | <u></u> |

| :::FIG                                                                                     |         |

| :::INTER<br>:::EXTP                                                                        |         |

| T Example :: simple transistor example                                                     |         |

| X, :: (enter description of formal pole/loop no. 1 here>                                   |         |

| Y/ :: <enter 2="" description="" formal="" here="" loop="" no.="" of="" pole=""></enter>   |         |

| P1 = 1, :: <enter 1="" description="" formal="" here="" no.="" of="" parameter=""></enter> |         |

| P2 = 2; :: <enter 2="" description="" formal="" here="" no.="" of="" parameter=""></enter> |         |

| : <enter body="" here="" model=""></enter>                                                 |         |

| :::DATA                                                                                    |         |

| = : : OR I G                                                                               |         |

| ::: <enter here="" model="" origin=""></enter>                                             |         |

| E0@;                                                                                       |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

|                                                                                            |         |

| Ready In 12, Col 1                                                                         |         |

#### 3. Fill in the Model File

The model file has to be filled in by

- Adding the pins (X, Y are replaced by the pin names)

- Adding the parameters (P1, P2 are replaced)

- Adding the transistor formula.

The pin currents are set by using an internal current source:

#### IG> J G = 0.0;

IG is the name of the current source, J is the current source identifier, G means, that the current is flowing from the pin G to the ground. The current value is zero. In such a way single pin currents can be set to certain values.

Since the i\_tr current flows from the drain to the source pin, one current source can be taken for both, the drain and the source pin:

IDS> J D S = i\_tr;

The result after filling in the model file is:

```

::<enter module description here>

:::SYMB

:::FIG

:::INTER

:::EXTP

T_Example :: simple transistor example

G,

:: Gate

:: Drain

D,

S / :: Source

P1=1, :: Threshold

P2 = 100, :: high conductance

P3 = .01; :: low<sup>~</sup>conductance

IG > J G = 0;

i_tr = (V.G>p1) * (V.D-V.S)*p2+

(V.G<=p1) * (V.D-V.S)*p3;

IDS> J D - S = i_t;

:::DATA

:::ORIG

:::<enter model origin here>

EO@;

```

This step is concluded by pressing  $\boldsymbol{O}\boldsymbol{K}$

#### 4. Create a symbol library

```

Press File > New

In the following window choose :

File type: symbol library

File name: T_Lib

Press OK

```

Then a window appears for graphical editing of a symbol of the transistor.

### 5. Design a symbol of the transistor

| Draw a picture which you want to use for the transistor within the red line.                                   |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Create the ports and connect it to the port names of the model:                                                |  |  |  |  |  |  |  |  |

| Press the <b>A</b> Button, put the connector to the correct place, and fill in the pin properties:             |  |  |  |  |  |  |  |  |

| Pin Properties: Name: D<br>Type: electric                                                                      |  |  |  |  |  |  |  |  |

| Press <b>OK</b><br>Click the symbol schematic in the left upper corner twice.<br>Change the symbol properties: |  |  |  |  |  |  |  |  |

| Symbol Properties: Name: T_Example                                                                             |  |  |  |  |  |  |  |  |

| Shortcut: T_E                                                                                                  |  |  |  |  |  |  |  |  |

| Type: @t_example                                                                                               |  |  |  |  |  |  |  |  |

| <b>Description:</b> simple transistor example                                                                  |  |  |  |  |  |  |  |  |

| Close the window.                                                                                              |  |  |  |  |  |  |  |  |

In our test case the symbol is a simple rectangle:

| DYNAST Shell - T_L<br>e Edit View Place | ib.Ibr<br><u>R</u> un <u>P</u> references <u>Wi</u> ndow <u>H</u> elp |           | _ 🗆                                   |

|-----------------------------------------|-----------------------------------------------------------------------|-----------|---------------------------------------|

| D 🖻 • 🗐 🎒                               | ∦ ⊫ ⊑   <u> </u>                                                      | <u> 1</u> |                                       |

| T_Lib.lbr                               |                                                                       |           |                                       |

|                                         | D                                                                     |           | · · · · ·                             |

|                                         |                                                                       |           |                                       |

|                                         |                                                                       |           | · · · · · · · · · · · · · · · · · · · |

|                                         | G                                                                     |           |                                       |

|                                         |                                                                       |           | · · · · · · · · · · · · · · · · · · · |

|                                         |                                                                       |           | · · · ·                               |

|                                         |                                                                       |           |                                       |

|                                         | 0                                                                     |           |                                       |

|                                         |                                                                       |           | · · ·                                 |

|                                         |                                                                       |           |                                       |

|                                         |                                                                       | 28, y=018 |                                       |

This is the window of the symbol properties:

| Symbol Pro          | ? ×                   |        |

|---------------------|-----------------------|--------|

| <u>N</u> ame        | T_Example             | OK     |

| <u>S</u> hortcut    | T_E                   | Cancel |

| <u>Т</u> уре        | @t_example            | Help   |

| <u>D</u> escription | simple transistor exa |        |

|                     |                       |        |

#### 6. Add comments to the transistor model

To complete the transistor modelling some comments should be added as it is adumbrated in the following model text:

```

:: simple transistor example

:::

::: Information for model documentation in latex formate ...

:::

:::INTER

:::EXTP

:::DATA

T_Example :: simple transistor example

G, :: Gate

D, :: Drain

S / :: Source

P1 = 1, :: Threshold

P2 = 100, :: high conductance

P3 = .01; :: low conductance

IG > J G = 0;

i_tr = (V.G>p1) * (V.D-V.S)*p2 +

(V.G<=p1) * (V.D-V.S)*p3;

ID> J D - S = i_tr;

E0@;

:::ORIG

:::Copyright in latex formate

```

Now the model is complete and can be used in any circuit!

#### 7. Create a circuit model

To create a circuit model the following step has to be done:

Press File > New

In the following window choose : *File type: problem text File name:* test1 *Title:* erster Test ...

Choose Standard template. Press  $\ensuremath{\textit{OK}}$

Then a text window appears to be edited. Additionally a diagram window can be opened, in which the transistor and other electrical models can be placed by drag and drop, and connected.

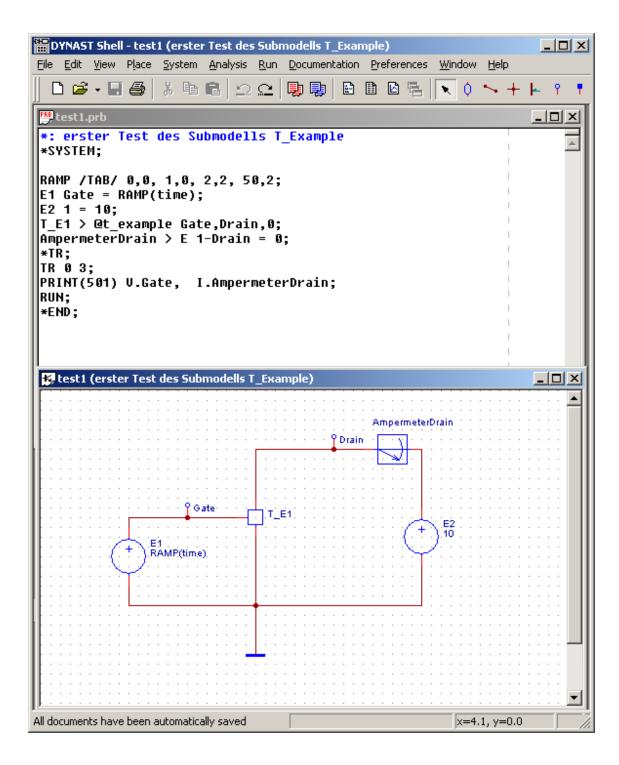

The model text and the circuit scheme are e.g. like this:

| _            |       |         | - testi   |         | Pur P     | Preferen | ces   | <u>W</u> indow | u Help  |                    |         |     |   |         |      | >     |

|--------------|-------|---------|-----------|---------|-----------|----------|-------|----------------|---------|--------------------|---------|-----|---|---------|------|-------|

|              |       |         |           |         |           |          |       |                |         |                    | Luu 🔤   |     | þ | B       | ≁  [ |       |

|              | est1. |         |           | 1       |           |          | _     |                |         |                    |         |     |   | 1       | 14   | _ 🗆 × |

|              | 🔳 G.  |         |           |         |           |          | erste | er Test d      | es Subm | odells T_I         | Example |     |   |         |      |       |

| 2.0-         |       | ate     |           |         |           |          |       |                |         |                    |         | /   |   |         |      |       |

| 1.8-<br>1.6- |       |         |           |         |           |          |       |                |         |                    | _/      |     |   |         |      |       |

| 1.0-<br>1.4- |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| 1.2-         |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| 1.0-         |       |         |           |         |           |          |       |                |         | /                  |         |     |   |         |      | <br>  |

| ).8-         |       |         |           |         |           |          |       |                | -       |                    |         |     |   |         |      |       |

| ).6-         |       |         |           | _       |           |          |       |                | /       |                    |         |     |   |         |      |       |

| ).4-         |       |         |           |         |           |          |       | /              |         |                    |         |     |   |         |      |       |

| ).2-<br>).0- |       |         |           |         |           |          | /     |                |         |                    |         |     |   |         |      |       |

|              | ■ 1.4 | Ampern  | neterDrai | in      |           |          |       |                |         | _                  |         |     |   |         |      |       |

| ).9-         |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| ).8-         |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| ).7-         |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      | <br>  |

| ).6-         |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| ).5-         |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| ).4-<br>1.3- |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| 13=<br>).2-  |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| ).1-         |       |         |           |         |           |          |       |                |         |                    |         |     |   |         |      |       |

| 0.0-         |       |         |           | 1       |           |          |       |                |         | 1                  |         |     |   |         |      | <br>  |

| C            | 0.0   |         |           | 0.5     |           |          | 1.0   |                | tim     | 1<br>1.5<br>1e [s] |         | 2.0 |   |         | 2.5  | 3)    |

| doc          | umen  | ts have | e been a  | utomati | ically sa | aved     |       |                |         |                    |         |     | x | =1.2, y | =0.1 |       |

The simulation results show that the drain current is jumping if the gate voltage becomes greater than one. It is caused by increasing the conductance from p3=0.01 to p2=100 at the same position. This example (netlist and simulator commands) can be found in the file InsertExercise2 - 1.prb.

## Module 3

# **Electronics of Semiconductor Structures**

#### Module units

| 3.1        | Char  | ge carriers in semiconductors                           |

|------------|-------|---------------------------------------------------------|

|            | 3.1.0 | Constants of semiconductor electronics                  |

|            | 3.1.1 | Electrons and holes in doped semiconductors             |

|            | 3.1.2 | Energy-band diagram                                     |

|            | 3.1.3 | Energy and potential dependency of charge carriers      |

|            | 3.1.4 | Temperature dependency of the charge carrier density 26 |

|            | 3.1.5 | Recombination                                           |

| <b>3.2</b> | Elect | ric field and space charges in semiconductors           |

| 3.3        | Char  | ge carrier transport in semiconductors                  |

|            | 3.3.0 | Summary                                                 |

|            | 3.3.1 | Field drift and diffusion currents 31                   |

|            | 3.3.2 | Carrier flow and the continuity equations               |

**Module overview.** The electronics of semiconductor devices is mainly based on mobile and fixed charges controlled by electric fields due to space charges within the semiconductor and supplied electrode potentials. Before analyzing the basics of the interaction between these quantities in a phenomenological manner, we have to be prepared on questions like

- What are the main differences between a semiconductor on the one hand and metallic conductors and insulators on the other hand?

- How to provide semiconductors purposefully with mobile carriers?

- How to make a semiconductor to a *p* -type or *n* -type conductor?

- What kind of charge carriers are available to carry a current in semiconductors?

- What makes the difference between free charges outside the semiconductor and such ones caught in a crystal lattice?

- Which phenomena are active to move carrier in semiconductors?

- How to find out the interaction between electric fields and charges in semiconductors?

This module is intended to give answers to these and other questions from a more phenomenological point of view. That means we are especially interested in providing modeling approaches rested on the basics of electronics as imparted in the curricula at the universities and advanced technical colleges. Moreover, it should be mentioned that the processing technology for semiconductor devices will be focused on dedicated results only without discussing details on how to perform such processes. So, we establish the basis for a widespread understanding of the working principles of the most important semiconductor devices.

#### Module objectives. After studying this module learners should:

- 1. Understand the basics necessary for an analytically oriented description of the operation principles of semiconductor devices.

- 2. Be acquainted with dedicated approaches proven in device modeling for years.

Module prerequisites. Basics in semiconductor physics and electronics

### 3.1 Charge carriers in semiconductors

#### 3.1.0 Constants of semiconductor electronics

| Absolute dielectric constant of the empty space | $\varepsilon_0 = 8.86 \times 10^{-12} As/Vm$  |

|-------------------------------------------------|-----------------------------------------------|

| Permittivity constant of Silicon $(Si)$         | $\varepsilon_H = 10^{-12} As / V cm$          |

| Relative dielectric constant $Si$               | $\varepsilon_{r_H} = 12$                      |

| Dielectric constant of Silicon oxide $(SiO_2)$  | $\varepsilon_{ox} = 3 \times 10^{-13} As/Vcm$ |

| Elementary charge                               | $q = 1.6 \times 10^{-19} As$                  |

| Free electron mass                              | $m_0 = 9.11 \times 10^{-31} kg$               |

| Energy gap of Si                                | $W_g = 1.1 \ eV$                              |

| Electron affinity of $Si$ against vacuum        | $W_{EA_{Si}} = 4.1 \ eV$                      |

| Electron affinity of $Si$ against $SiO_2$       | $W_{EA_{SiO_2}} = 3.25 \ eV$                  |

| Planck's constant h                             | $h = 6.63 \times 10^{34} W s^2$               |

| Boltzmann's constantk                           | $k = 1.38 \times 10^{-23} Ws/K$               |

| Reference temperature                           | $T_0 = 300 \ K$                               |

| Thermal voltage $V_T$                           | $V_T (300 K) = 25.9 mV$                       |

| Effective density of states in conduction band  | $N_C \approx 10^{19} cm^{-3}$                 |

| Effective density of states in valence band     | $N_V \approx 10^{19} cm^{-3}$                 |

| Intrinsic density for $Si$                      | $n_i (300 \ K) = 1.5 \times 10^{-10} cm^{-3}$ |

| Diffusion coefficient for electrons in $Si$     | $D_n \approx 40 \ cm^2/s$                     |

| Diffusion coefficient for holes in $Si$         | $D_p \approx 10 \ cm^2/s$                     |

| Averaged electron lifetime in $Si$              | $\tau_n \approx 10^{-9} \ s$                  |

| Averaged hole lifetime in $Si$                  | $\tau_p \approx 10^{-7} \ s$                  |

| Space charge layer carrier life time            | $\tau_s \approx 10^{-9} \ s$                  |

| Forward floating potential for $Si$ diodes      | $V_{FO} \approx 0.7 V$                        |

#### 3.1.1 Electrons and holes in doped semiconductors

Generally, particle currents in semiconductors rely on two sorts of mobile carriers, the electrons and defect electrons (so-called holes). Electrons and holes carry the elementary charge -q and  $q = 1.6 \times 10^{-19} As$ , respectively. Because these carriers are caught in a crystal lattice, they are interactions with the ionized atoms fixed in the crystal lattice.

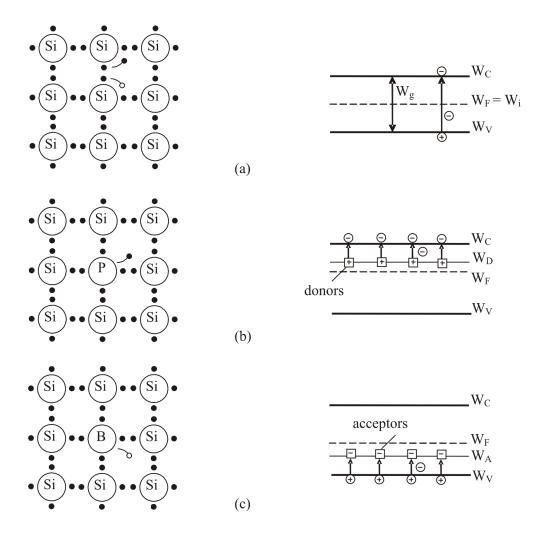

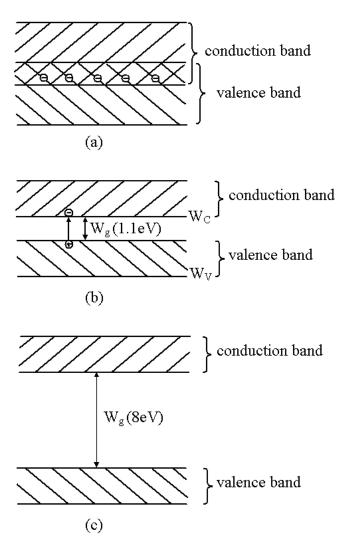

That is why they are not "free", rather than "quasi-free". Basically, the carriers in crystals are influenced by electric fields (forces) externally imposed on the semiconductor, as well as by internal fields due to the ionized atoms of the lattice. Therefore, they exhibit characteristics which differ from them of fee carriers. To keep formally at the approach developed for supplied external forces (fields), we have to involve such internal interactions implicitly at least. Thus, we use the carrier's effective mass  $(m_n$  and  $m_p$ ) instead of the their free carrier mass  $m_{0n}$  and  $m_{0p}$ , respectively. The effective mass can be derived from the energy band structure of semiconductors. Based on the wave-particle-dualism, globally, the band structure describes some characteristics of the "wave behavior" of quanta in semiconductors. In fact, semiconductors exhibit anisotropic band structures, i.e. the effective mass of electrons and holes are tensors. Another important difference to free carriers concerns their energy. Generally, free carriers can accept unlimited energy levels, however, that is not true for carriers in crystals. Due to the internal interactions with the ionized lattice atoms, the electrons and holes in solids may only reach restricted values of energy. In particular, there is a material-specific energy band gap  $W_g$  (forbidden energy band) for electron and holes. It separates the conduction band with the lower band edge  $W_C$  from the valence band with the upper band edge  $W_V$  (see Figure 3.1), i.e.  $W_g = W_C - W_V > 0$ .

Figure 3.1: 2D lattice structure (schematically) [2]

At room temperature the forbidden energy gap between  $W_C$  and  $W_V$  is  $W_g = 1.1 \ eV$  for silicon Si. Basically, carriers in undoped semiconductors (intrinsic semiconductors) are generated in pairs by thermal exciting valence band electrons. Leaving the valence band and entering the conduction band, each of the thermally excited electrons generates a (mobile) hole in the valence band (see Figure 3.1(a)). Both, the electrons lifted into the conduction band and the defect electrons (holes) left behind the valence band will contribute to a current flow. Generally, this kind of intrinsic conductivity is negligible compared to the conductivity due to ionized impurities [1], [2].

In this case, impurity atoms with a valency of five (so-called donors like phosphorus (P) or arsenic (As)) and a valency of three (called acceptors e.g. boron (B)) replace purposefully some silicon (Si) atoms in the crystal lattice, respectively. If the donors and acceptors get ionized, each donor delivers an electron to the conduction band, and each acceptor will capture an electron from the valence band leaving a defect electron (hole) behind. Really, to be executed, these ionization processes only need the comparably small energy difference  $\Delta W_D > W_C - W_D > 0$  respective  $\Delta W_A > W_A - W_V > 0$  (see Figure 3.1(b), (c)). In this way two important phenomena occur. On the one hand, excess electrons and holes will be delivered by ionized donors and acceptors, turning the semiconductor to an n-type or p-type conductor. On the other hand, the ionized positively charged donors and the negatively charged acceptors fixed in the lattice create space charges which have to be considered for the modeling of internal electronics in semiconductor devices. The latter item will be discussed in the next paragraphs in more details.

Normally, at room temperature all donors (density  $N_D$ ) and acceptors (concentration  $N_A$ ) are ionized. Consequently, in an *n*-type semiconductor doped with donors  $N_D$  the electron density is approximately  $n = N_D^+ \approx N_D$  where the intrinsic concentration  $n_i$  can be neglected ( $n_i \ll N_D$ ).

For a p-type semiconductor the hole concentration becomes  $p = N_A^- \approx N_A$  since  $n_i \ll N_A$  (see Figure 3.8) [2].

#### 3.1.2 Energy-band diagram

As mentioned above electrons and holes in semiconductors exhibit dedicated characteristics, like acceptance of only restricted energy levels, effective mass, etc. Some of them can be illustrated with the band structure of semiconductors and its energy-band diagram. Whereas the band structure (already mentioned above) shows important conclusions found out by quantum-mechanic analysis, generally, an energy-band diagram presents dedicated energy levels (among others the band edges  $W_C$  and  $W_V$ ) against the location described with a position coordinate (x, y or z) of a Cartesian system. To illustrate the increase of electron energy in the energy-band diagram, usually the ordinate with an arbitrary reference level is used for that.

Before going in details, we should mention what the band model's positive features are. As we will demonstrate with examples below, in particular, the energy-band diagram is used to detect where space charges, electric fields and currents will occur within the semiconductor. Moreover, it is very useful to find out the right (internal) boundary conditions needed to calculate the potential and field distribution within the semiconductor device structures. In this way a problem of the complex contact electronics can be defused drastically for modeling purposes. Last but not least, based on it we are able to explain in a phenomenological manner the operating principle of complex semiconductor devices without a detailed analysis of the internal electrons.

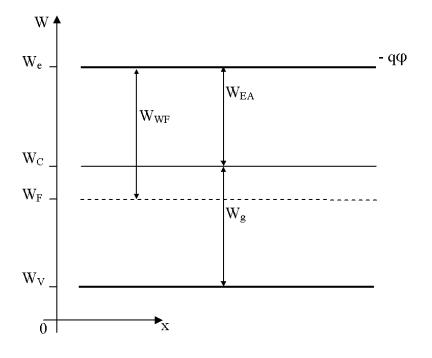

Mostly, only the three energy levels (the band edges  $W_C$ ,  $W_V$  and the Fermi-level  $W_F$ ) as well as the potential energy of a fee unmoved electron ( $W_e$ ), and additionally, the two energy differences (the electron affinity  $W_{EA}$  and work function  $W_{WF}$ ) are sufficient to complete the energy-band model as demonstrated in the following.

From the band-structure we know that just energy levels near the band edges  $W_C$  and  $W_V$  are most interesting for the existence of electrons and holes in semiconductors. That is why just these levels have to be pictured. As mentioned above, from them we find the energy gap  $W_g = W_C - W_V$ .

If we have doped semiconductors, we still need the position of the so-called Fermi-level  $W_F$  in the energy band diagram. The Fermi-edge  $W_F$  is an important formal parameter which characterizes the occupation probability of available energy states in the conduction and valence band with electrons or holes (see also paragraph 3.1.3). The position of the energy level  $W_F$  in the band model is dependent on the impurity concentration. Normally, the Fermi-level is within the forbidden band (see Figure 3.1). Such semiconductors are said to be non-degenerated. Otherwise, in heavily doped semiconductors  $(N_D > 10^{19} cm^{-3})$  or  $N_A > 10^{19} cm^{-3}$ ) the  $W_F$  level can dip into the conduction or valence band (degenerated semiconductors).

Characteristically, under thermal equilibrium (that means e.g. without currents in the semiconductor) the Fermi-edge  $W_F$  is constant versus the position coordinate throughout the energy-band model (e.g.  $\frac{d}{dx}W_F = 0$ ). In this case, there is only one energy level  $W_F$  for electrons and holes. However, in an unbalanced thermo-dynamic state (e.g. with current flow due to supplied voltages) the Fermi-level is split-up into a quasi-Fermi-level for electrons  $W_{F\_n}$ , and another one for holes  $W_{F\_p}$ . Normally, both levels vary differently versus the position coordinate.

It should be mentioned, that the energy equivalent  $q \cdot V$  of a supplied voltage V has to meet the condition  $q \cdot V = W_{F_n} - W_{F_p}$ .

More details on how to posit  $W_F$  in the energy-band diagram, and about  $W_{F_n}$  and  $W_{F_p}$  as well as their potential equivalents  $\psi_n$  and  $\psi_p$  will be given in the following paragraphs.

To find out locations where space charges and electric fields dominate the internal electronics in semiconductors; additionally, we need information on changing the electrostatic (macro) potential against the position coordinate. Therefore, the energy equivalent of the electrostatic (macro) potential, i.e. the level of potential energy is also pictured in the band diagram (see Figure 3.2).

Figure 3.2: Energy-band diagram [1], [2]

Because the energy difference between the energy equivalent of the macro potential  $W_e = -q \cdot \varphi > 0$  and the band edges  $W_C$  and  $W_V$  is only dependent on the crystal characteristics, the potential  $W_e$  and the band edges remain in parallel throughout the structure as long as the crystal's characteristics (e.g. the semiconductor material) do not change.

Regarding to  $W_e$ , we are able to make visible two essential energy differences, namely, the electron affinity  $W_{EA}$  and the work function  $W_{WF}$  (see Figure 3.2).

The energy necessary to free an electron from the conduction band edge  $W_C$  is called electron affinity  $W_{EA}$ . In other words,  $W_{EA} = W_e - W_C > 0$ , where  $W_e = -q \cdot \varphi > 0$  is the potential energy of a resting and free electron outside of crystals.

In particular, for modeling electronic devices in Si technology, we need  $W_{EA\_Si} = 4.1 \ eV$  and  $W_{EA\_SiO_2} = 3.25 \ eV$ . These energy values are necessary to emit an electron into vacuum and silicon oxide, respectively.

The energy difference between  $W_e$  (energy equivalent to the macro potential  $\varphi$ ) and  $W_F$  (Fermi-level) is called work function  $W_{WF}$ , which is a material-specific parameter.

We know, for doped semiconductors  $W_F$  is dependent on the impurity concentration, and consequently  $W_{H\_Si}$ , too. In particular, we should distinguish between  $W_{H\_Si\_p}$  and  $W_{H\_Si\_n}$  for p - and n -doped semiconductors.

Based on the energy quantities pictured in the energy band diagram and their relative position to each other we are able to distill consequences out of the energy-band diagram for metals, semiconductors and insulators.

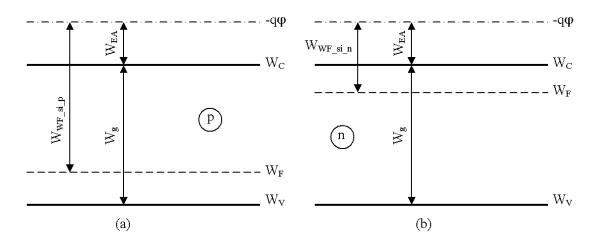

Figure 3.3: Energy band diagram: (a) metal, (b) semiconductor, (c) insulator [2]

As shown in Figure 3.3(a), metals have no forbidden band, because the valence band overlaps the conduction band. Consequently, in metals all electrons will contribute to the comparably high conductivity.

Contrarily, an insulator (see Figure 3.3(c)), is characterized by a large energy gap. Therefore, a relatively high energy is necessary to lift valence band electrons into the conduction band. That is why the thermal generation of carriers is extremely weak and at room temperature pretty unlikely, i.e. no mobile charges are available within the insulator.

The semiconductor (see Figure 3.3(b)) is neither as a good conductor as the metals are, nor an insulator. The particularity exploited for electronic devices is due to its small intrinsic conductivity, which can be prepared goal-oriented by doping.

To meet the expectations and to illustrate the explanation given above, the energy-band diagram of a p - and n -doped semiconductor under thermal equilibrium will be presented at first (see Figure 3.4).

Obviously, the main differences between these energy-band diagrams concern the relative position of the Fermi-level  $W_F$  within the forbidden band, and consequently, the work function  $W_{WF}$  of the p-and n-type semiconductor.

Figure 3.4: Energy band diagram of a p - and n -doped semiconductor [1], [2]

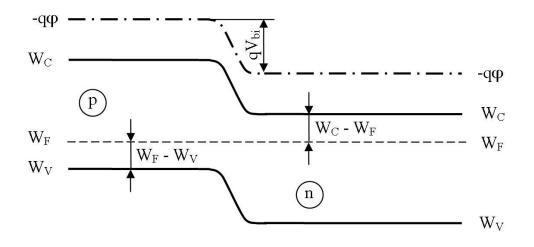

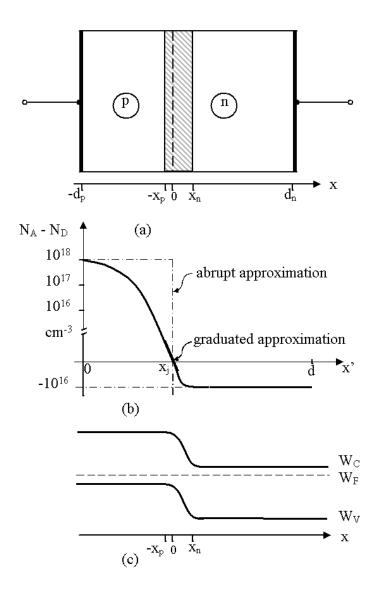

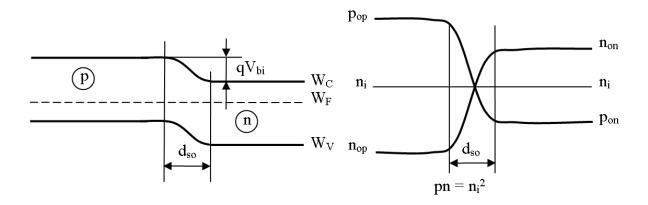

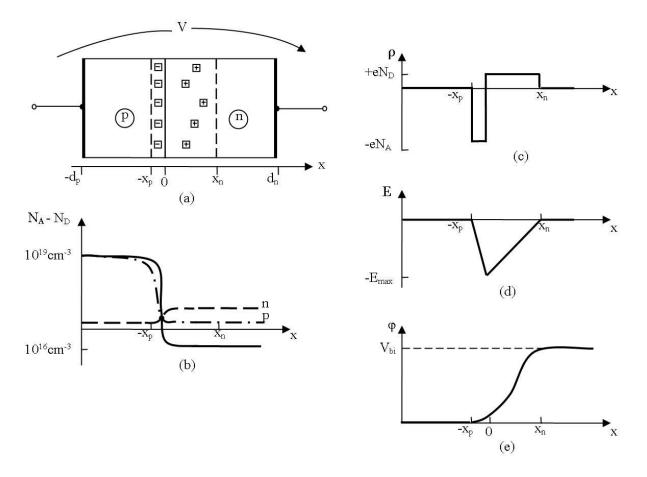

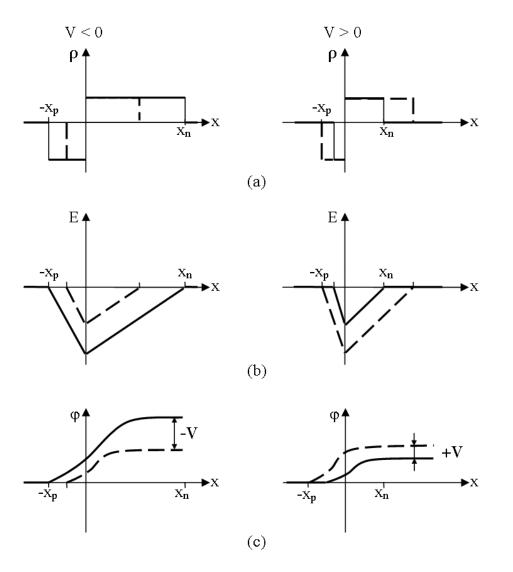

If we physically implement a p - and n -type semiconductor layer in the same crystal, a so-called pn -junction is formed. To construct its energy-band model we have to bring together the band-diagrams given in Figure 3.4(a) and (b), carefully. In doing so we should consider that  $W_F$  is constant throughout the structure. In fact, there are no interface and dipole charges at the stoichiometric junction where the conducting type is technologically changed from p -type to n -type or vice verse. That is why the electrostatic potential within the structure may not exhibit any discontinuities. As mentioned above, the energy equivalent to the electrostatic potential has to stay in parallel to the band edges. Consequently, careful combining the energy-band diagrams of a p - and n -type semiconductor layer results in energy-band diagram of a pn -junction as shown in Figure 3.5.

Figure 3.5: Energy-band diagram of a pn-junction [1], [2]

Without any analytic calculations we can learn from it, that within a small region around the junction from a p - to an n -type semiconductor  $(x_j)$  the electrostatic potential varies with the x -coordinate. Below (e.g. see paragraph 3.2) we will show, that this fact signalizes an electric field due to space charges in this region. Moreover, caused by this electric field an internal (built-in) potential difference  $V_{bi}$  occurs, which has to be considered for determining the potential and field distribution within the structure correctly.

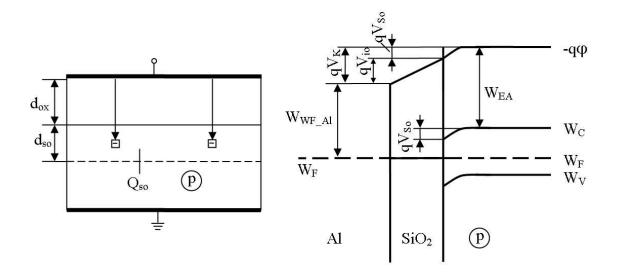

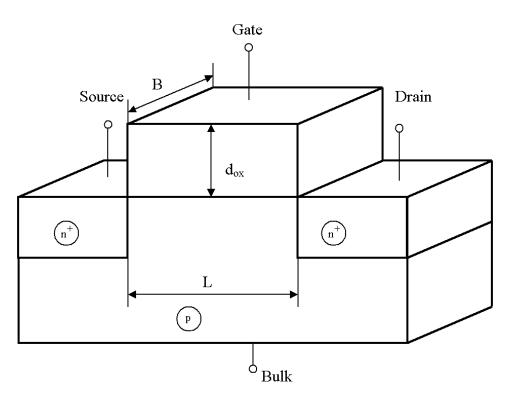

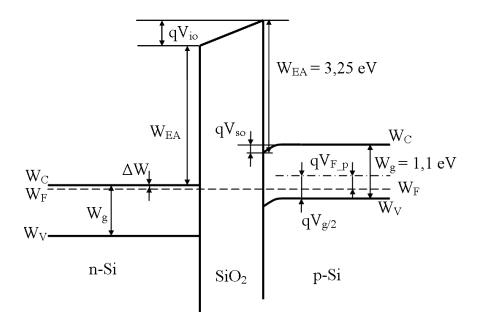

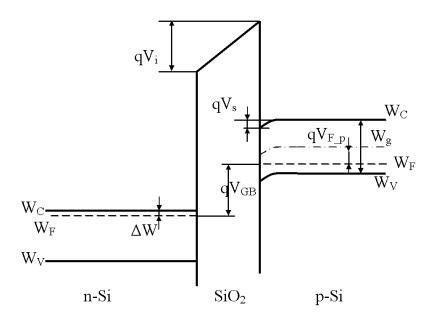

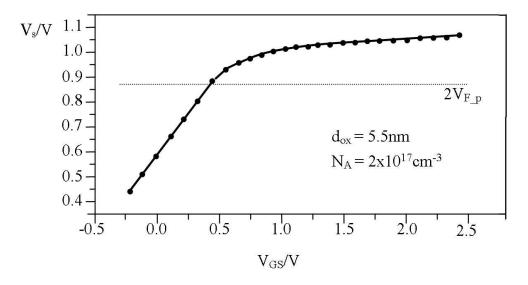

Another important basic structure of semiconductor devices is the MOS-structure shown in Figure 3.6 for a p-doped semiconductor.

Figure 3.6: Energy-band diagram of a MOS-structure under thermal equilibrium

In our example we assume, that the gate is made from aluminum Al.

To come up with the energy band diagram of such a MOS-structure we need the band model for the gate metal (Al) and the p-doped semiconductor. Simply, the metal's energy-band model is given with the Fermi-level  $W_F$  and its work function  $W_{WF\_Al}$ . Separated by a very thin  $SiO_2$  layer a p-doped semiconductor completes the MOS-structure where the semiconductor's band model is well-known already.

Once again, we have to make sure that under thermal equilibrium conditions  $W_F$  is constant throughout the complete structure (see Figure 3.6).

Due to the difference in the work function of Si ( $W_{WF\_Si\_p}$ ) and Al ( $W_{WF\_Al}$ ) we get a linear increase of the potential (potential energy) within the  $SiO_2$  insulator layer. Supposed there are no interface charges located at the interface between the insulator and semiconductor, the electrostatic potential and its slope (the slope corresponds to the electric field as discussed in paragraph 3.2), may not exhibit any kind of discontinuities at the interface. Moreover, deep in the semiconductor, i.e. in a sufficient distance from the interface between oxide and semiconductor, the MOS-structure's energy-band diagram has to agree with that of a p-doped semiconductor. Therefore, we have to accept the band bending as shown in Figure 3.6. Finally,  $W_{EA\_SiO_2}$  gives the energy difference to  $W_C$ , wherewith the energy-band diagram of the MOS structure can easily be completed, supposed all relevant rules given above are considered carefully.

To sum up what we can learn from this example, we should recognize the following:

Already under thermal equilibrium (i.e. without supplied voltages) we can identify a space charge at the interface between  $SiO_2$  and Si. Roughly speaking, this space charge layer ( $Q_{s0}$  with the layer width  $d_{s0}$ ) is due to complex phenomena of contact electronics and leads to a electric field built-in the oxide and also in the semiconductor. Consequently, a drop of potential across the oxide ( $V_{i0}$ ) as well as the semiconductor ( $V_{s0}$ ) will occur. The sum of these voltages is the so-called contact potential  $V_K$ , which plays an important role to define the correct boundary conditions for a detailed analysis of the potential and field distribution within the MOS structure with power supply.

#### 3.1.3 Energy and potential dependency of charge carriers

To calculate the energy distribution of electrons and holes in semiconductors, at first, we need the density  $D_C(W)$  and  $D_V(W)$  of energy levels W in the conduction and valence band available to be occupied with electrons and holes, respectively. Indeed, a quantum-mechanics-based analysis of the semiconductor's band structure results in  $D_C(W)$  and  $D_V(W)$  with the so-called effective density of states in the conduction and valence band  $N_C$  and  $N_V$ . These are given by

$$N_C = 2 \cdot \left(\frac{2 \cdot \pi \cdot m_n \cdot k \cdot T}{h^2}\right)^{\frac{3}{2}} \approx 10^{19} \ cm^{-3} \tag{3.1}$$

and

$$N_V = 2 \cdot \left(\frac{2 \cdot \pi \cdot m_p \cdot k \cdot T}{h^2}\right)^{\frac{3}{2}} \approx 10^{19} \ cm^{-3}$$

(3.2)

where h is Planck's constant, k is Boltzmann's constant, T stands for the absolute temperature, and  $m_n$ ,  $m_p$  is the effective mass of electrons and holes, respectively.

Secondly, we have to consider the Fermi-Dirac-statistics for the occupation of states with electrons and holes. Generally, the occupation probability f(W) for a state with the energy W by an electron is

$$f(W) = \left(1 + e^{\frac{W - W_F}{k \cdot T}}\right)^{-1} \tag{3.3}$$

where  $W_F$  is the well-known Fermi-level (see paragraph 3.1.2). Consequently, for defect electrons (holes) we have to replace f(W) by 1 - f(W).

Integrating  $D_C(W) \cdot f(W)$  and  $D_V(W) \cdot (1 - f(W))$  over the conduction and valance band, respectively, we find the energy distribution of electrons (density  $n_0$ ) and holes (concentration  $p_0$ ) under thermal equilibrium conditions. Finally, for non-degenerated semiconductors ( $n_0 < N_C$  and  $p_0 < N_V$ ) we get for electrons

$$n_0 = N_C \cdot e^{-\frac{W_C - W_F}{k \cdot T}},\tag{3.4}$$

and

$$p_0 = N_V \cdot e^{-\frac{W_F - W_V}{k \cdot T}}$$

(3.5)

for holes. Using Equations (3.4) and (3.5) we find the intrinsic density  $n_i$  from the product

$$n_i^2 = n_0 \cdot p_0 = N_C \cdot N_V \cdot e^{-\frac{W_g}{k \cdot T}}$$

(3.6)

The intrinsic density  $n_i$  is a typical material parameter with a strong temperature dependency. At room temperature, the intrinsic density is  $n_i (300 \text{ K}) = 1.5 \times 10^{-10} \text{ cm}^{-3}$  in Si. For more information see paragraph 3.1.4.

For instance, at room temperatures in a p-type semiconductor is  $p_{0p} \approx N_A >> n_{0p} = \frac{n_i^2}{p_{0p}}$ . That is why in a p-type semiconductor the holes  $(p_{0p})$  are called the majority carriers, and consequently, the electrons are the minority carriers. In an n-type semiconductor the electrons  $(n_{0n})$  are the majority carriers and the holes  $(p_{0n})$  are in the minority.

In paragraph 3.1.2 we have already learned that the band edges  $W_C$  and  $W_A$  run in parallel to the electrostatic potential as long as there are no any discontinuities (e.g. dipole-charges would cause potential discontinuities) occur. Moreover, we should remember that a single Fermi-level  $W_F$  for electrons and holes makes only sense in thermal equilibrium, i.e. without currents due to supplied voltages. Otherwise, we have to take into account a quasi-Fermi-level  $W_{F_n}$  for electrons and  $W_{F_p}$  for holes. Their potential equivalents are  $W_{F_n} = -q \cdot \psi_n$  and  $W_{F_p} = -q \cdot \psi_p$ . Therewith and under consideration of Equation (3.6) we find the potential representation of the carrier density:

$$n = n_i \cdot e^{\frac{\varphi - \psi_n}{V_T}} \tag{3.7}$$

and

$$p = n_i \cdot e^{\frac{\psi_p - \varphi}{V_T}}.$$

(3.8)

where  $V_T$  is the so-called thermal voltage. It follows from

$$V_T = \frac{k \cdot T}{q} \qquad \qquad V_T (300 \ K) \approx 25.9 \ mV \tag{3.9}$$

As we will see below, the Equation (3.7) and (3.8) play an essential role for modeling the internal electronics of semiconductor devices.

#### 3.1.4 Temperature dependency of the charge carrier density

Typically, semiconductors are strongly dependent on the temperature T. Apart from the electrostatic potential  $\varphi$ , all other quantities of the carrier densities n and p (see Equation (3.7) and (3.8)) are more or less strongly dependent on T. In particular the intrinsic density has an exponential temperature dependency

$$n_i(T) = \sqrt{N_C(T) \cdot N_V(T)} \cdot e^{-\frac{W_g(T)}{2 \cdot k \cdot T}}.$$

(3.10)

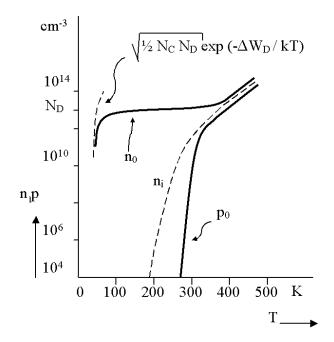

As measured by the exponential increasing of  $n_i$  with heating, the temperature influence on the energy gap (forbidden band)  $W_g(T)$  as well as on the effective density of states in the conduction and valence band  $N_C(T) \propto T^{3/2}$  and  $N_V(T) \propto T^{3/2}$  is comparably weak (see Equations (3.1) and (3.2)). To come to acceptable results for our modeling purposes, we should discuss the temperature dependence of electrons and holes in an *n*-doped semiconductor under thermal equilibrium as given in Figure 3.7.

Figure 3.7: Temperature dependency of carriers in an n-doped semiconductor [2]

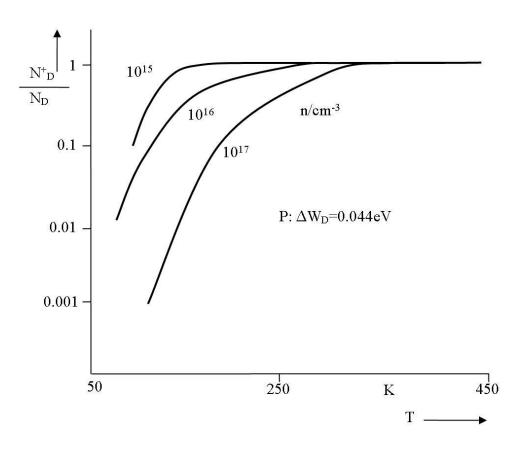

At very low temperatures the electron concentration  $n_{0n}$  is pretty small, however, it increases exponentially with rising temperatures. In this low temperature range (e.g. T < 100 K) a lot of donors has not been ionized yet, i.e.  $p_{0n} \ll n_{0n} \ll N_D$  (see Figure 3.8).

Figure 3.8: Temperature dependency of ionization [2]

At room temperatures the ionization process is completed, and we have  $p_{0n} \ll N_D$ . For electronic application, just this temperature range is of greatest interest.

At high temperatures (e.g. T > 350 K) the thermal generation of carrier pairs will dominate, and the semiconductor is increasingly losing its typical difference between minority and majority carriers.

#### 3.1.5 Recombination

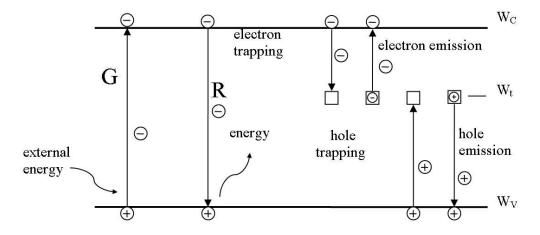

If the semiconductor is supplied with "external" energy (e.g. by heating) or it may absorb photons with an energy  $h \cdot f > W_g$  (f: photon's frequency) and an appropriate impulse, valence band electrons will be lifted into the conduction band. Thus, pairs of electrons and holes will be generated and characterized by the rate G. This rate G describes the number of generated electron-hole pairs per unit time and volume. As generation processes play an important role in advanced electronic devices (laser, light emitting diodes (LED)), the opposite process to generation, called recombination appears in all semiconductor-based devices more or less.

The recombination rate R gives the number of electron-hole pairs recombined (disappeared) per unit time and volume. Both mechanisms the generation and the recombination are schematically illustrated in Figure 3.9.

Figure 3.9: Generation and recombination in semiconductors [2]

Principally, there is a wide-variety of recombination mechanisms. However, at the moment we are only interested in the so-called indirect recombination performed via energy states within the band gap. Under steady state conditions electrons and holes are trapped at the same rate by such energy states (traps).

If anywhere in the semiconductor the carrier densities differ from their concentration under thermal equilibrium ( $\Delta n = n - n_0$  and  $\Delta p = p - p_0$ ), and moreover, these derivations are sufficiently small ( $\Delta n \ll n_0$  and  $\Delta p \ll p_0$ ) we obtain

$$R = \frac{\Delta n}{\tau_n} = \frac{\Delta p}{\tau_p} \tag{3.11}$$

for the recombination rate where  $\tau_n$  and  $\tau_p$  are the averaged electron and hole lifetime until to their recombination. The lifetime is a very complex parameter affected by the semiconductor material, the doping, the temperature and last but not least from the carrier concentration. For estimation purposes we use  $\tau_n \approx 10^{-9}s$  and  $\tau_p \approx 10^{-7}s$ .

#### Self-Assessment Questions

#### Question 3.1.1:

What type of impurities has to be used to make an *n*-type semiconductor, donors or acceptors?

#### Question 3.1.2:

What energy levels are necessarily needed to pivture an energy-band diagram of a *p*-type semiconductor under thermal equilibrium conditions?

#### Question 3.1.3:

What is the meaning of the quantities  $n, n_i, \varphi, \psi_n$  and  $V_T$  of  $n = n_i \cdot e^{\frac{\varphi - \psi_n}{V_T}}$ ?

#### Question 3.1.4:

What kind of termerature dependency is essential for the intrinsic density  $n_i$ ?

### 3.2 Electric field and space charges in semiconductors

Basically, the operation principles of most electronic devices are mainly based on mobile and fixed charges as well as currents due to moved charge carries. To move mobile carriers in semiconductors, basically, two reasons have to be considered, the electric field and the diffusion, respectively. Generally, the electric and magnetic fields have also to be taken into account if we intend to model electronic device's functionality on phenomenological basics. Therefore, the modeling process needs considering Maxwell's equations. Application-driven, we are particularly interested in solving modeling problems where the time rate of changing the magnetic field is not too high. That means we may assume that the electric field  $\vec{E}$  does not have curls caused by fast varying the magnetic field with the time, i.e.

$$curl \ \vec{E} = \vec{0}.\tag{3.12}$$

In this time regime the vector  $\vec{E}$  can be derived from an electrostatic potential field  $\varphi(\vec{r})$  by the space derivation with respect to the position vector  $\vec{r} = \vec{i} \cdot x + \vec{j} \cdot y + \vec{k} \cdot z$ :

$$\vec{E} = -grad \varphi = -\left(\vec{i} \cdot \frac{\partial}{\partial x}\varphi + \vec{j} \cdot \frac{\partial}{\partial x}\varphi + \vec{k} \cdot \frac{\partial}{\partial z}\varphi\right).$$

(3.13)

$\vec{i}$ ,  $\vec{j}$  and  $\vec{k}$  are the unit vectors to the space coordinates of a Cartesian coordinate system.

Supposed the electric field  $\vec{E}$  is curl-free, generally, it originates from and terminates on charges. Therefore, charges are said to be the sources of the electrostatic fields. For instance, it can be due to space charges and also charges on interface with material discontinuities as well as on electrodes. So, an electric field is built-up between electrodes supplied with different potentials. In this case,  $\vec{E}$  originates from positive surface charges on the electrode connected to the positive pole of the power supply and terminates on the negative surface charges on the electrode connected to the negative pole. To detect the sources of electric fields in a space, Maxwell's system prescribes the vector operation divergence:

$$div\,\vec{D} = \frac{\partial}{\partial x}\left(\vec{D}\cdot\vec{i}\right) + \frac{\partial}{\partial x}\left(\vec{D}\cdot\vec{j}\right) + \frac{\partial}{\partial z}\left(\vec{D}\cdot\vec{k}\right) = \rho \tag{3.14}$$

where  $\vec{D}$  denotes the vector of electric displacement and  $\rho$  is the space charge density.

Equation (3.14) is the differential form of Gauss' low

$$\oint_{(A)} \vec{D} \cdot d\vec{A} = \int_{(V)} div \vec{D} \cdot dV = \int_{(V)} \rho \cdot dV.$$

(3.15)

Basically, the vector element  $d\vec{A}$  of the closed surface A with the interior volume V is directed outwards. The vectors  $\vec{E}$  and  $\vec{D}$  are not independent from each other, in fact, it yields

$$\vec{D} = \varepsilon \cdot \vec{E} = \varepsilon_0 \cdot \varepsilon_r \cdot \vec{E}. \tag{3.16}$$

where  $\varepsilon$  is the material's permittivity with the absolute dielectric constant  $\varepsilon_0 = 8.86 \times 10^{-12} As/Vm$  of the empty space and the relative dielectric constant  $\varepsilon_r$  typical for the material's dielectric characteristic.

For Si we use the permittivity constant  $\varepsilon_H = 10^{-12} As/Vcm$ , whereas the dielectric constant for silicon oxide  $(SiO_2)$  is given by  $\varepsilon_{ox} = 3 \times 10^{-13} As/Vcm$ .

Generally,  $\varepsilon$  is a tensor, but in most applications we use the material's permittivity as scalar parameter.

Inserting Equation (3.16) with Equation (3.13) in Equation (3.14) we obtain

$$div\,\vec{D} = -\varepsilon \cdot div\,(grad\,\,\varphi) = -\varepsilon \cdot \left(\frac{\partial^2}{\partial x^2}\varphi + \frac{\partial^2}{\partial y^2}\varphi + \frac{\partial^2}{\partial z^2}\varphi\right) = \rho \tag{3.17}$$

and finally, from Equation (3.17) Poisson's equation in its well-known fashion:

$$\Delta \varphi = \frac{\partial^2}{\partial x^2} \varphi + \frac{\partial^2}{\partial y^2} \varphi + \frac{\partial^2}{\partial z^2} \varphi = -\frac{\rho}{\varepsilon}.$$

(3.18)

To be solved application-specifically, this second order partial differential equation needs boundary conditions, i.e. so-called boundary problems have to be defined. Depending on the kind of boundary conditions to be met, basically, we distinguish between three basic boundary problems. To tackle these tasks is the main goal of the potential theory in mathematics. Actually, most of our modeling approaches demand solutions of the Dirichlet's problems where the potential on the boundary has to be specified before solving the Poisson's equation. Basically, the Dirichlet's problem can formally be solved by Green's function, which is typical for the geometry of the field space surrounded with boundaries provided with specified potentials.

Unfortunately, this approach does not meet our modeling demands sufficiently because the Green's function is unknown for most practical applications, and typically, the boundary problems for dedicated modeling problems in electronics require additional assumptions. In particular, there is a remarkable difference to electrostatics where the space charges and boundary potentials are specified and fixed before solving Poisson's equation. In our modeling tasks, often, we have to involve the strong interaction between charges and electric field. Because of charge neutrality, usually, no space charges appear before applying the electric field. Imposing an electric field on a semiconductor, space charges are coming out, and will interact with this field. For instance, this kind of modeling problems has to be solved for determining the width of the space charge layer of a pn-junction (e.g. see paragraph 4). Moreover, if mobile charges ought to be included in the modeling procedure, in many cases we have to consider their exponential dependency in terms of the potential  $\varphi$  to be determined. In such cases the problems become even nonlinear, and we have to find out physically-founded additional conditions to make these problems analytically solvable. Anyway, the calculation of electronic fields in semiconductor structures is really more complex than in the classic electrostatics. Below, we will demonstrate our approach on how to calculate the field and potential distribution in a pn-junction and a MOS structure, respectively.

### Self-Assessment Question

#### Question 3.2:

What is the Poisson's differential equation needed for?

### 3.3 Charge carrier transport in semiconductors

#### 3.3.0 Summary

Basically, the currents in semiconductors are composed of two components, namely, the convection current resulting from moved carriers, and the displacement current due to the time-variable changing the displacement vector field  $\vec{D}$ . Apart from the dynamics of the mobile carrier's assembling and rebuilding processes at very high frequencies (RF-range), mostly the entire device electronics can be analyzed under neglecting the displacement current. Indeed, holes and electrons can contribute to the current in semiconductors. Each of these carriers may be moved by an electric field and/or by diffusion due to a density gradient of the carriers. That is why we have to consider two transport equations (holes and electrons), and each with both current components, the field drift part and the diffusion component.

The electric field interacts with all charges in the semiconductor. Therefore, we have to take into account as space charges as the charge carriers. That makes the analysis non-linear and highly complex.

Based on Maxwell's equations only the total current density must be sources free. Consequently, this constrain has not to be applied to the electron and hole current. Therefore, for these carrier currents we may accept sources (carrier generation) and sinks (carrier recombination), if the carrier generation and recombination processes take place in pairs. This approach leads to two continuity equations (one for holes and one for electrons) which make sure the Maxwell's requirements.

The following paragraph is aimed at a phenomenological description of the carrier transport in semiconductors included interactions between carrier density and the electric field and electrostatic potential, respectively.

#### 3.3.1 Field drift and diffusion currents

The carrier (or convection) current density  $\vec{S}$  in semiconductors arises from mobile space charges of holes with the concentration  $\rho_p = q \cdot p$  and electrons with the density  $\rho_n = -q \cdot n$  moved with the velocities  $\vec{v}_P$ and  $\vec{v}_N$ , respectively. The density vector  $\vec{S}$  is given by

$$\vec{S} = \vec{S}_p + \vec{S}_n = \rho_p \cdot \vec{v}_P + \rho_n \cdot \vec{v}_N.$$

(3.19)

Generally, drift fields and/or diffusion processes are the reason for carrier moving velocities. Whereas the drift components (carrier velocity  $\vec{v}_p$  or  $\vec{v}_n$ ) come from an electric drift field  $\vec{E}$ , the diffusion parts (carrier velocities  $\vec{v}_{p-D}$  and  $\vec{v}_{n-D}$ ) originate from carrier density gradients (grad p and grad n).

For our modeling approaches we are especially interested in carrier drift due to relatively weak electric fields. At low electric fields the drift velocities  $\vec{v}_p$  and  $\vec{v}_n$  are proportional to the field  $\vec{E}$ :

$$\vec{v}_p = \mu_p \cdot \vec{E} \tag{3.20}$$

and

$$\vec{v}_n = -\mu_n \cdot \vec{E}. \tag{3.21}$$

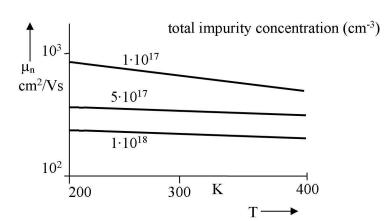

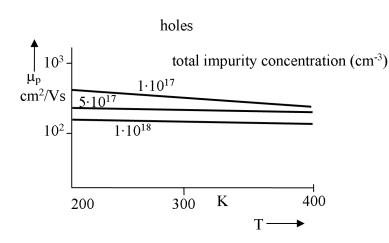

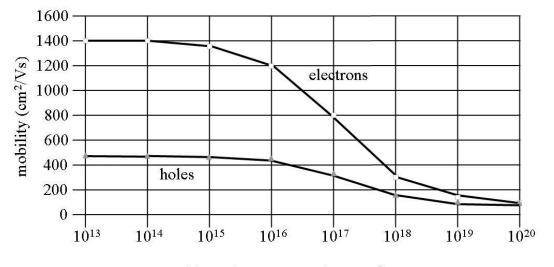

The mobility  $\mu_n$  for electrons and  $\mu_p$  of holes is dependent on the temperature T and the total impurity concentration as shown in Figure 3.10, 3.11 and Figure 3.12.

electrons

Figure 3.10:  $\mu_n$  's temperature dependency in Si [2]

Figure 3.11:  $\mu_p$  's temperature dependency in Si [2]

total impurity concentration  $(cm^{-3})$

Figure 3.12:  $\mu_n$  and  $\mu_p$  in dependency on the total impurity concentration [5]

Because of the scattering mechanisms, the carrier mobilities decrease also at high electric fields. Therefore, the drift velocity of electrons and holes saturates, and the simple mobility models given by Equation (3.20) and Equation (3.21) need qualifying.

The second velocity components  $\vec{v}_{p_D}$  and  $\vec{v}_{n_D}$  are due to diffusion, and are given by

$$\vec{v}_{p_D} = -D_p \cdot \frac{grad \ p}{p} = -D_p \cdot grad \ \ln \frac{p}{n_i}$$

(3.22)

and

$$\vec{v}_{n_D} = -D_n \cdot \frac{grad \ n}{n} = -D_n \cdot grad \ \ln \frac{n}{n_i}$$

(3.23)

$D_p$  and  $D_n$  are the diffusion coefficient for holes and electrons, respectively. For medium-doped silicon we have  $D_p\approx 10~cm^2/s$  and  $D_n\approx 40~cm^2/s$ .

Using Equations (3.19) to (3.23) we obtain the transport equation for holes  $\vec{S}_p$  and electrons  $\vec{S}_n$ :

$$\vec{S}_p = \rho_p \cdot \vec{v}_P = \rho_p \cdot (\vec{v}_p + \vec{v}_{p_D}) = q \cdot \left(\mu_p \cdot p \cdot \vec{E} - D_p \cdot grad \ p\right)$$

(3.24)

and

$$\vec{S}_n = \rho_n \cdot \vec{v}_N = \rho_n \cdot (\vec{v}_n + \vec{v}_{n_D}) = q \cdot \left(\mu_n \cdot n \cdot \vec{E} + D_n \cdot grad n\right)$$

(3.25)

If the density of mobile carriers is very high (e.g. in metallic conductors) only a relatively small electric field is needed to transport any demanded current. In such cases, the diffusion contributions to the total convection current can be neglected, and we find from Equation (3.24) and Equation (3.25)

$$\vec{S} = \vec{S}_p + \vec{S}_n = \rho_p \cdot \vec{v}_p + \rho_n \cdot \vec{v}_n = q \cdot (\mu_n \cdot n + \mu_p \cdot p) \cdot \vec{E} = \kappa \cdot \vec{E}$$

(3.26)

where  $\kappa$  is the conductor's conductivity given by

$$\kappa = q \cdot (\mu_n \cdot n + \mu_p \cdot p). \tag{3.27}$$

Supposed the carrier densities and their mobilities are independent on the electric field, the right part of Equation (3.26) can be interpreted as "Ohm's law" for semiconductors whose conductivity is majority carrier controlled.

In general, the carrier mobility and the diffusion coefficient for holes and electrons are not independent from each other. In fact, the Einstein's relation yields

$$\frac{D_p}{\mu_p} = \frac{D_n}{\mu_n} = V_T = \frac{k \cdot T}{q}$$

(3.28)

where  $V_T$  is the thermal voltage well-known from Equation (3.9).

Using Equation (3.28) and  $\vec{E} = -grad \varphi$  (see Equation (3.13)) the drift and diffusion part of the hole and electron current density can be combined in a single equation for each. Let us take the hole current as an example. We find

$$\vec{S}_p = -q \cdot \mu_p \cdot p \cdot grad\left(\varphi + V_T \cdot \ln \frac{p}{n_i}\right) = -q \cdot \mu_p \cdot p \cdot grad \ \psi_p \tag{3.29}$$

In an analog way we determine for the electron current density

$$\vec{S}_n = -q \cdot \mu_n \cdot n \cdot grad\left(\varphi - V_T \cdot \ln \frac{n}{n_i}\right) = -q \cdot \mu_n \cdot n \cdot grad \psi_n \tag{3.30}$$

where

$$\psi_p = \varphi + V_T \cdot \ln \frac{p}{n_i} \tag{3.31}$$

and

$$\psi_n = \varphi - V_T \cdot \ln \frac{n}{n_i} \tag{3.32}$$

is the quasi-Fermi potential for holes and electrons, respectively.

Basically, from Equation (3.29) and Equation (3.30) we learn that current flow compels the variation of the quasi-Fermi potentials along the local coordinates. Without any current is

$$\psi_p = \psi_n = \Psi_F \tag{3.33}$$

where  $\Psi_F$  is the potential equivalent of the Fermi-level.

From Equation (3.31) and Equation (3.32) we extract the hole and electron concentration in a semiconductor with an electric field and a carrier density gradient inside. We obtain the Equations (3.7) and (3.8) The carrier's dependency on the electrostatic potential  $\varphi$  as well as the quasi-Fermi potential  $\psi_p$ ,  $\psi_n$  is extremely helpful in analyzing the field and potential distribution in semiconductor structures by Poisson's equation.

#### 3.3.2 Carrier flow and the continuity equations

From Maxwell's theory we know, the total current (density  $\vec{S}_t$ ) is composed of a convection current part (density $\vec{S}$ ) and the displacement current (density $\vec{S}_D$ )

$$\vec{S}_t = \vec{S} + \vec{S}_D.$$

(3.34)

Whereas  $\vec{S}$  describes the charge transport by moved carriers (electron and holes), the displacement current is due to the time-variable changing the displacement vector  $\frac{\partial}{\partial t}\vec{D}$ . Based on Maxwell's equations, the total current  $\vec{S}_t$  has to be free of sources. Using the divergence operator div () and considering the Equations (3.19) and (3.14) as well as the space charges for holes  $\rho_p = q \cdot p$  and electrons  $\rho_n = -q \cdot n$ , formally, we get

$$div \ \vec{S}_t = div \ \vec{S} + div \ \vec{S}_D = div \ \left(\vec{S}_p + \vec{S}_n\right) + \frac{\partial}{\partial t} \left(\rho_p + \rho_n\right) = 0.$$

(3.35)

Principally, in semiconductors we have to take generation and recombination processes into account. As mentioned in paragraph 3.1.5, these mechanisms are executed pair-wise. From the phenomenological point of view, these processes will have an influence on the electron and hole current, however, they may not break Maxwell's equation on the continuity of  $\vec{S}_t$ , i.e.  $div \ \vec{S}_t = 0$ . Therewith, we can derive from Equation (3.35) the so-called continuity equations for the electron and hole current. Finally, we achieve

$$div \ \vec{S}_n = -q \cdot (G - R) + q \frac{\partial}{\partial t} n \tag{3.36}$$

for the electron current, and

$$div \ \vec{S}_p = q \cdot (G - R) - q \cdot \frac{\partial}{\partial t} p.$$

(3.37)

for the hole current where G and R stand for the generation and recombination rate.

With appropriate models for generation and recombination (e.g. see Equation(3.11)), and using the transport equations (see Equations (3.24) and (3.25)) as well as the field distribution (e.g. derived from the solution of Poisson's equation), the continuity equations (3.36) and (3.37) describe the dynamics (assembly and rebuilding) of the carrier distributions in semiconductors. We will use them to model the internal electronics, in particular the minority carrier distribution within bipolar devices.

#### Self-Assessment Questions

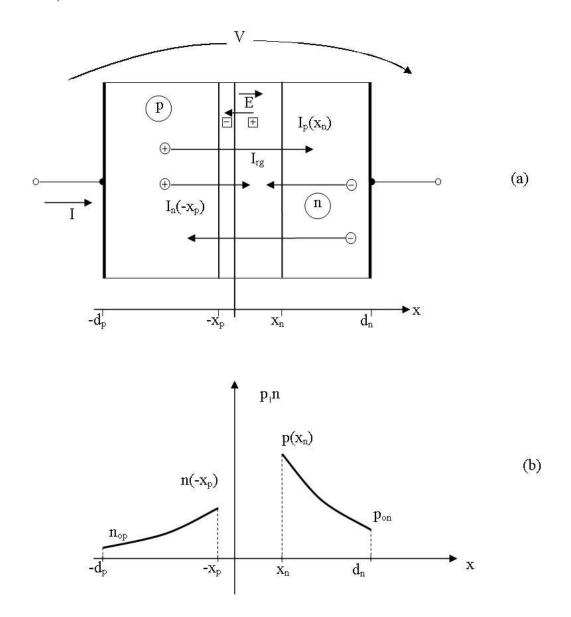

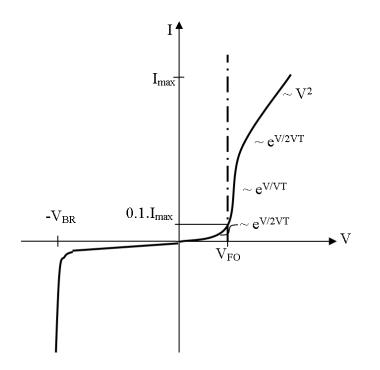

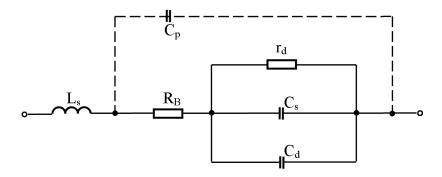

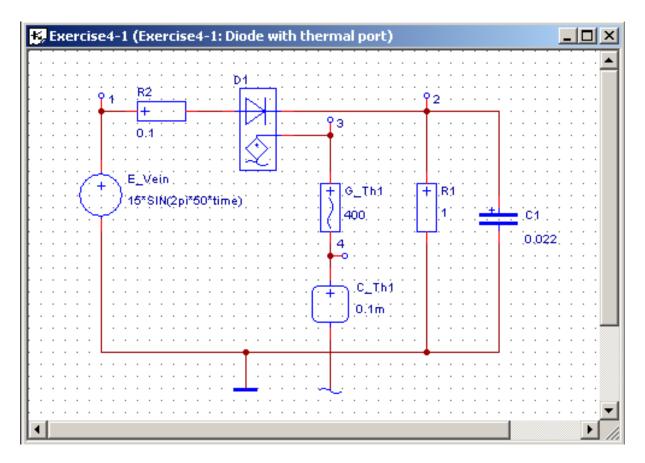

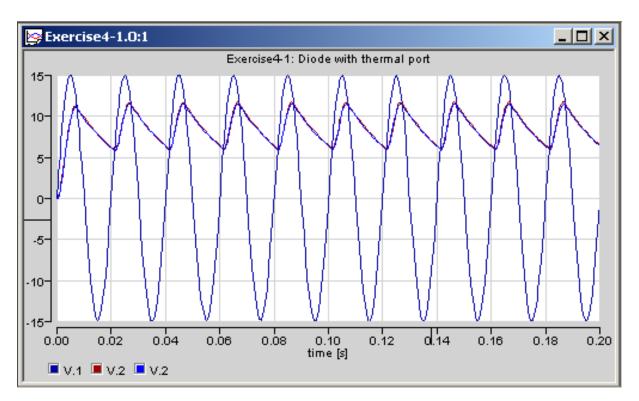

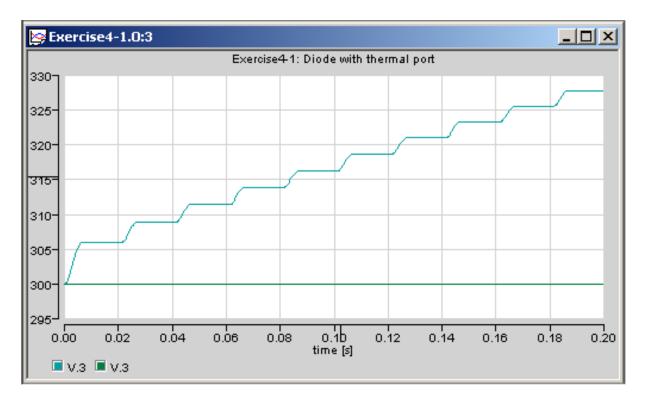

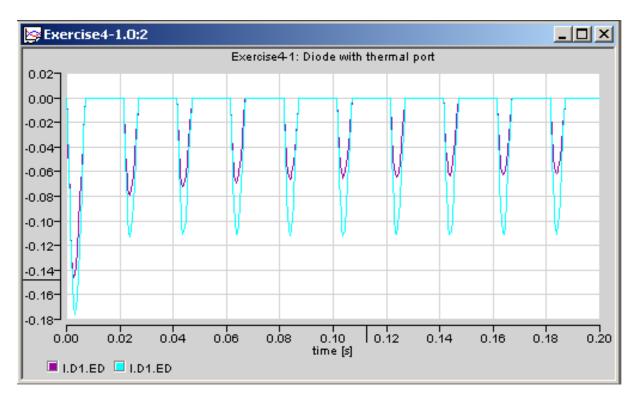

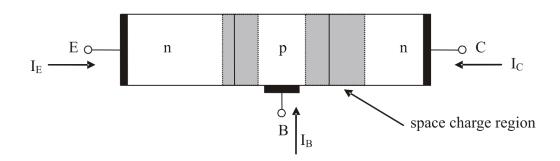

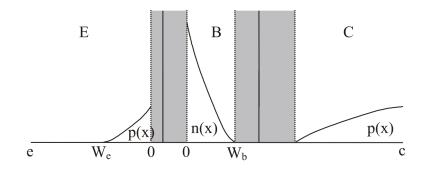

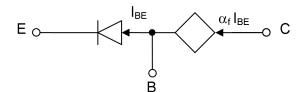

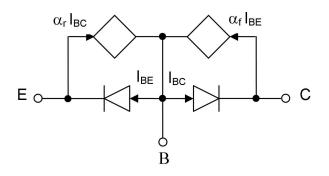

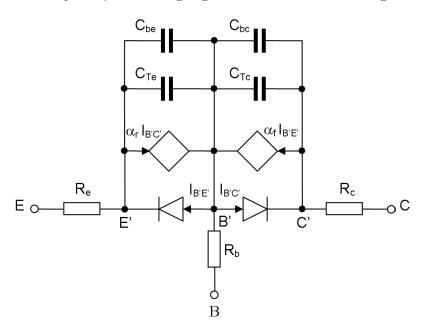

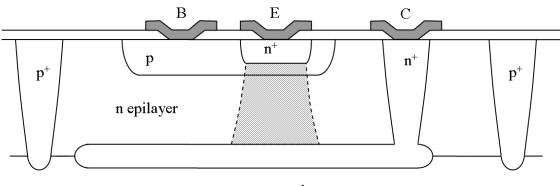

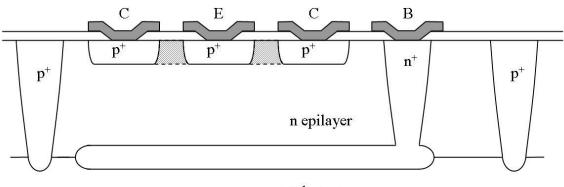

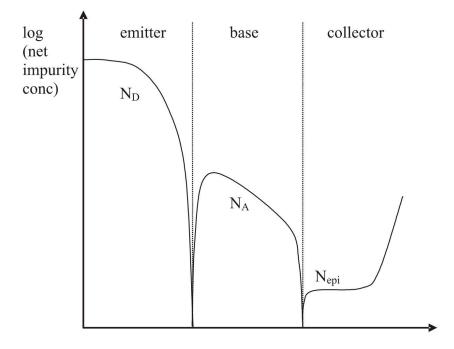

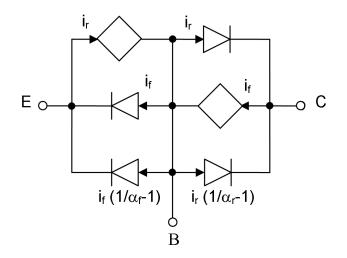

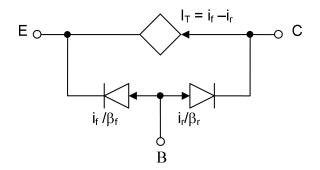

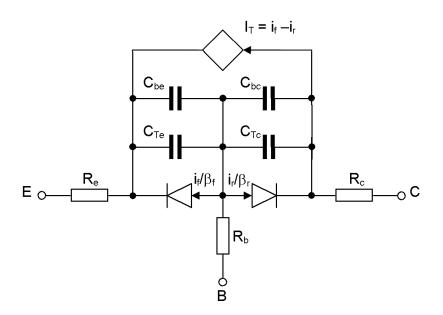

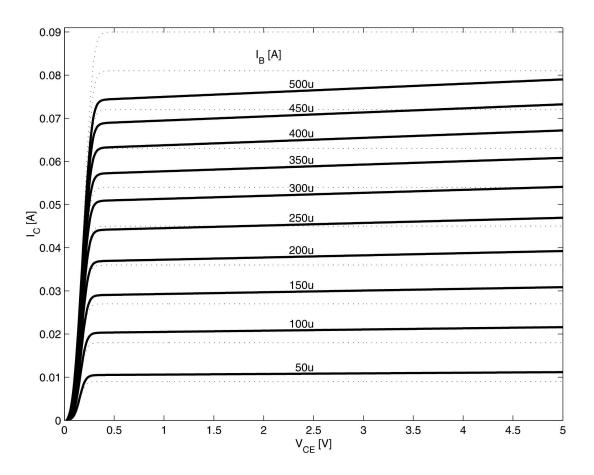

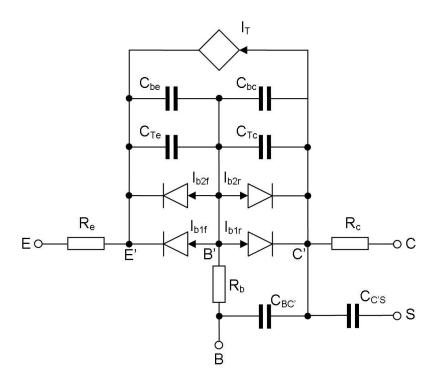

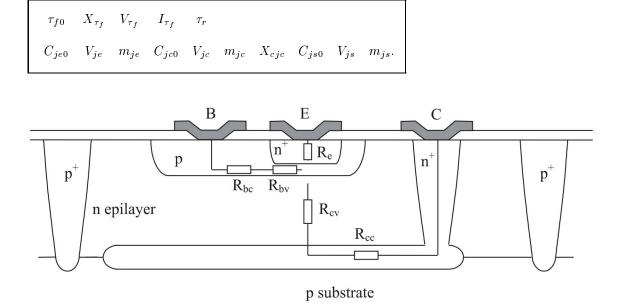

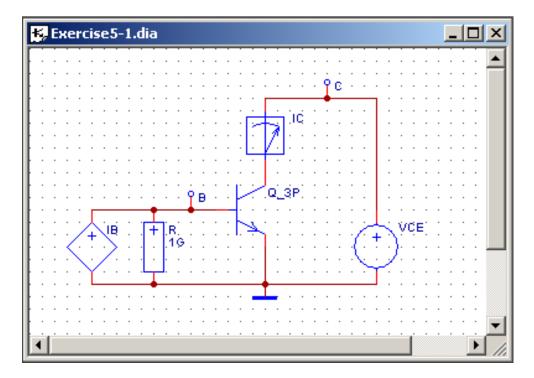

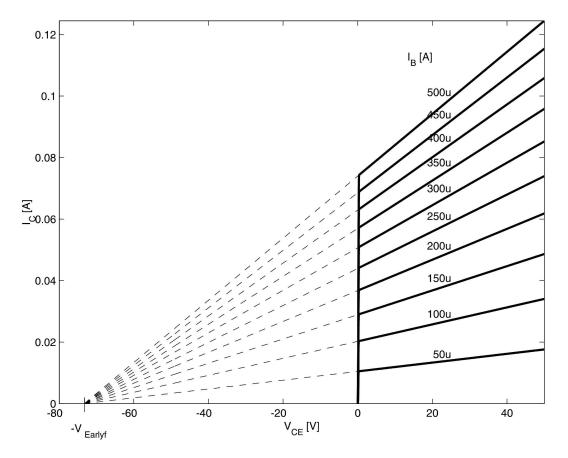

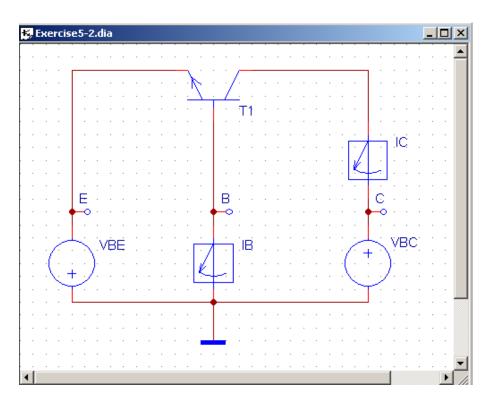

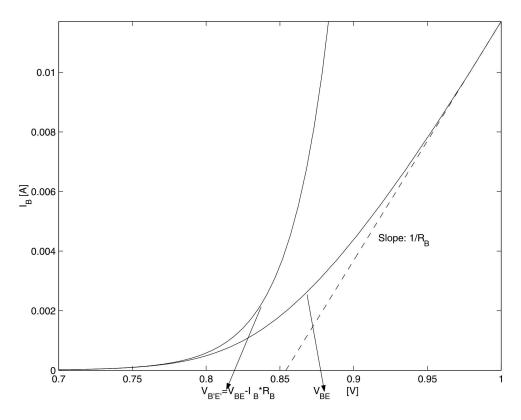

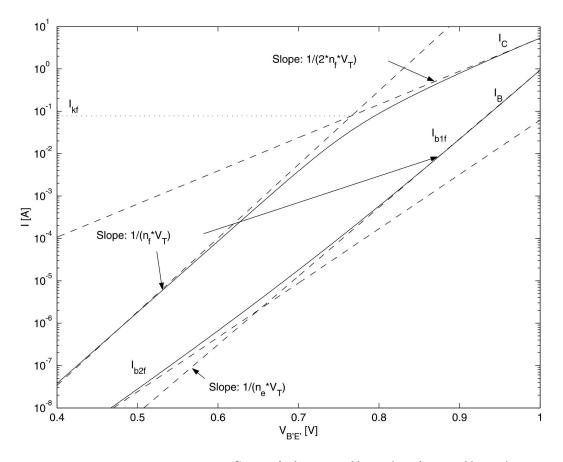

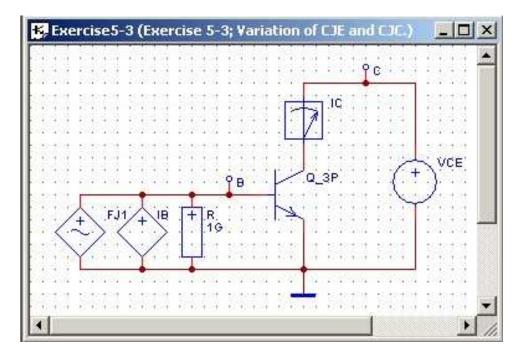

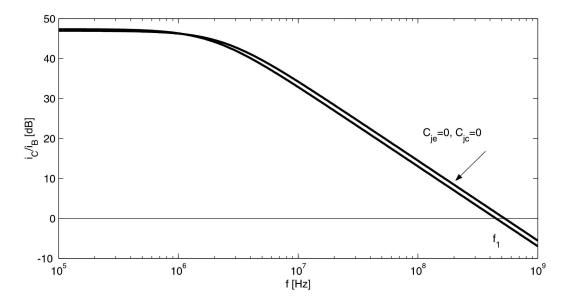

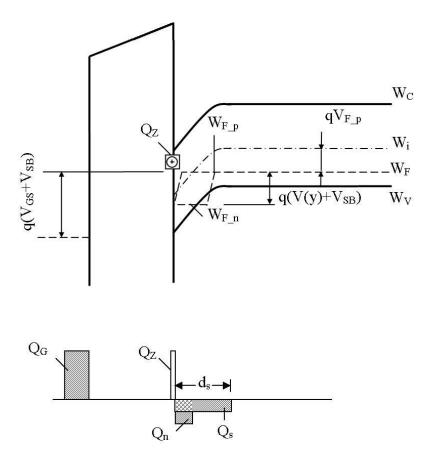

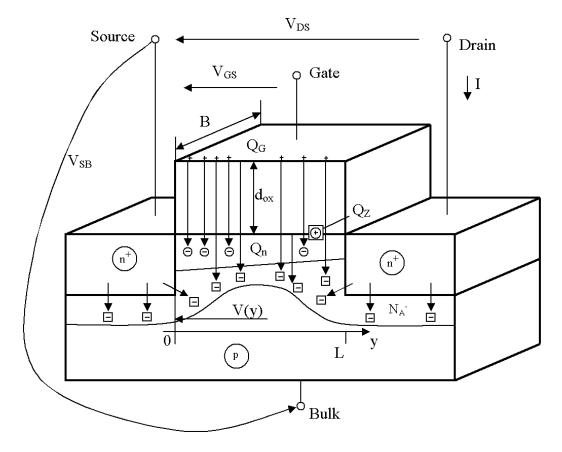

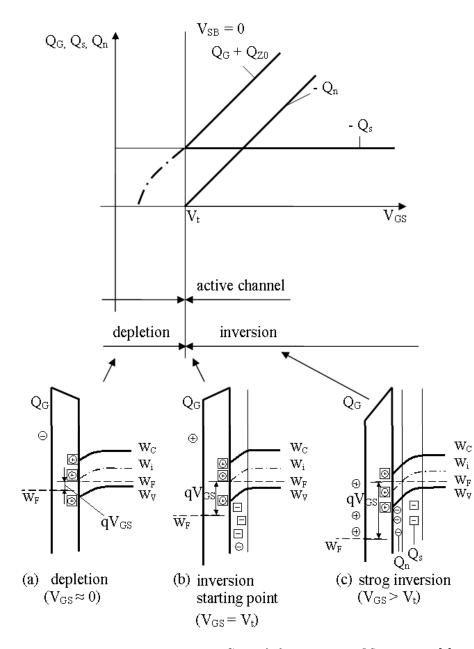

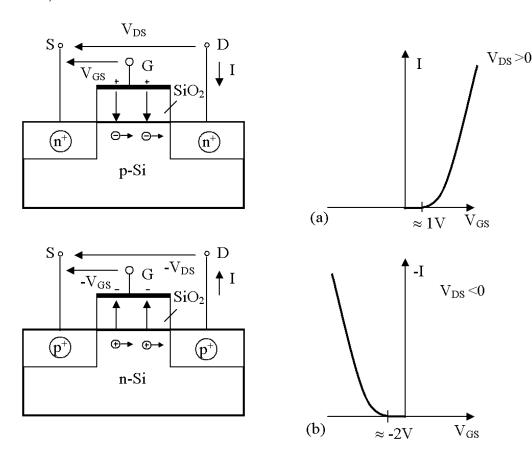

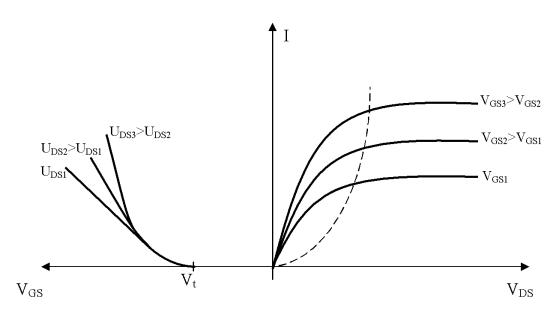

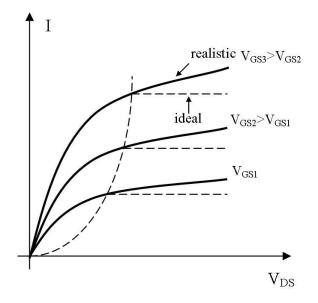

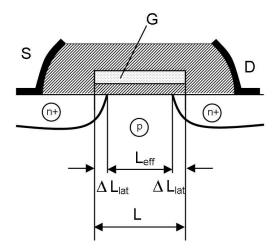

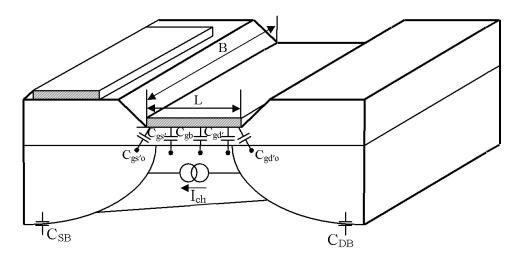

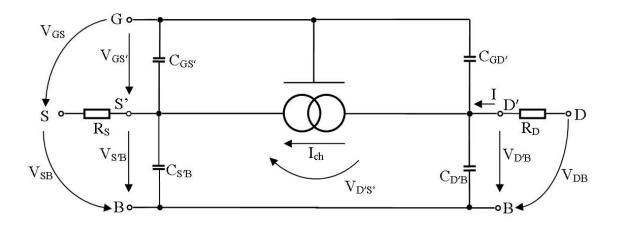

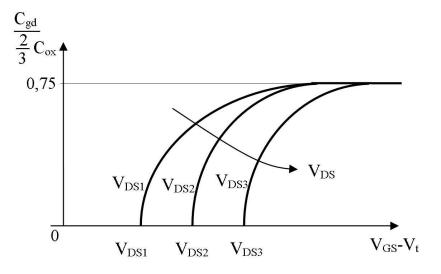

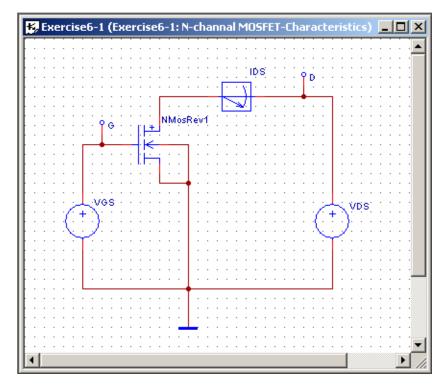

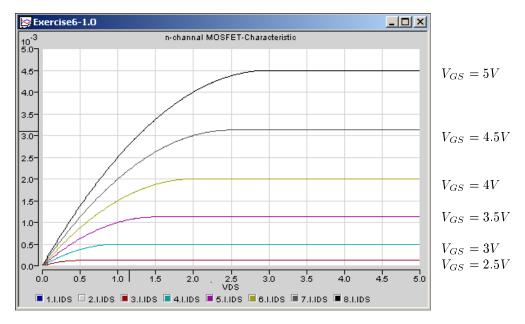

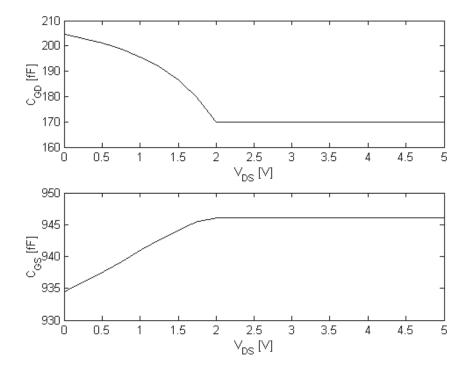

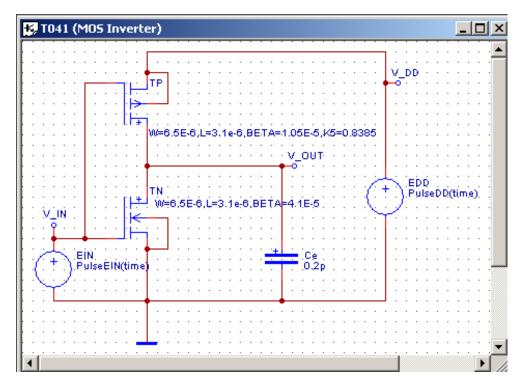

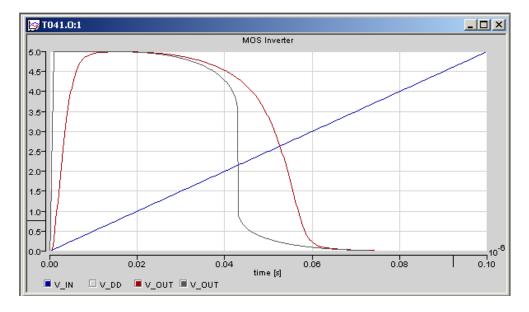

#### Q 3.3.1: